Published in 2020

27th IEEE ICECS

Mirror Full Adder

SET Susceptibility

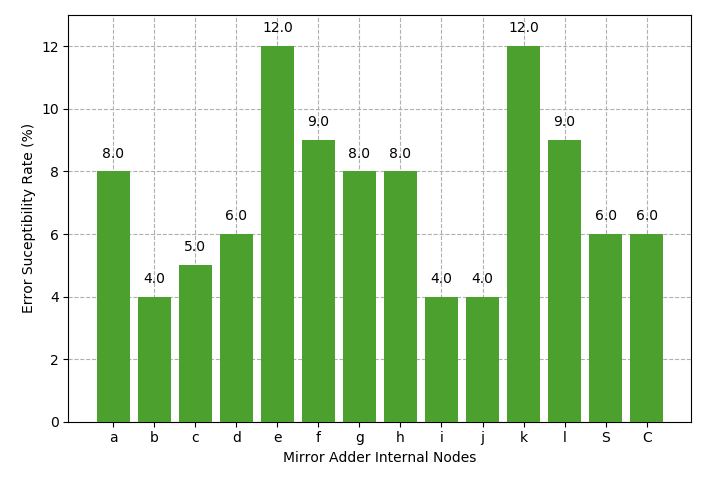

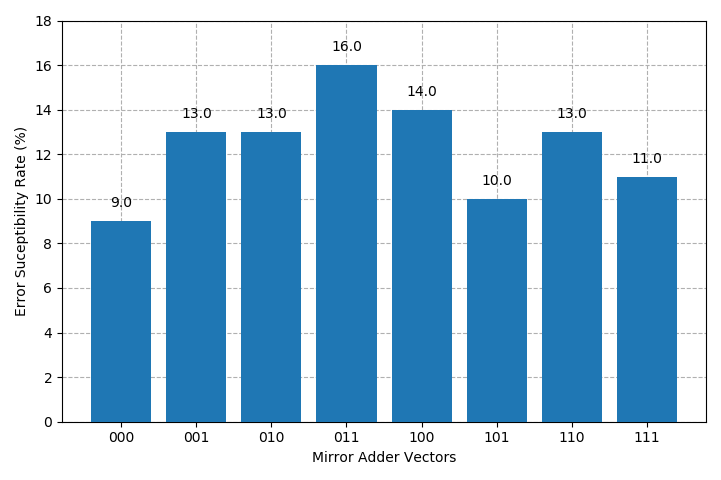

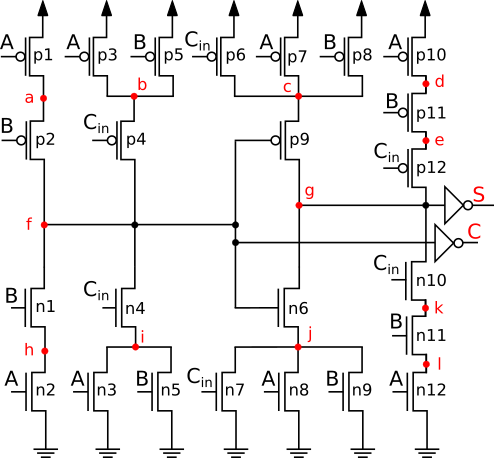

This work investigates the Mirror full adder circuit using a 7nm FinFET technology, considering the SET susceptibility and the robustness of all internal nodes of the circuit. This work aims to identify how this full adder topology behaves in a specific environment, observing the charge collected at each internal node. The devices involved in the processing of the carry-out function shown to be more robust than the Sum circuit and also presented a lower error rate. Furthermore, the input vector 000 proved to be the most critical one, among the input combinations, and the results show a dependence of the type of pulse in the generation of errors in the Mirror full adder.

A comparative analysis of SET occurrence and radiation sensitivity of the Mirror full adder are introduced in this paper. It was found, analytically, that the most susceptible nodes to generates an error are the e and k, and they are closely related to the Sum output. The nodes g and j are the most sensitive nodes presenting the lowest LETth results, showing that there are internal nodes more sensitive than the output nodes. The vector more susceptible to generates an error is $001$. However, the vector 000 presented the lowest LETth, being the critical input combination for the Mirror. Also, it is possible to conclude that the pulse type 101 is more responsible for generating errors in the FA analyzed.